# MODEL NO. BL1602A1WRNBU\$ VER.01

FOR MESSRS:

ON DATE OF:

APPROVED BY:

BOLYMIN, INC.

5F, No. 38, Keya Rd., Daya Dist., Central Taiwan Science Park, Taichung City, 42881, Taiwan. Web Site:<u>http://www.bolymin.com.tw</u> TEL:+886-4-25658689 FAX:+886-4-25658698

# History of Version

| Version | Contents    | Date       | Note  |

|---------|-------------|------------|-------|

| 01      | NEW VERSION | 2017/07/28 | SPEC. |

|         |             |            |       |

|         |             |            |       |

|         |             |            |       |

|         |             | ЛЛ         | NI    |

|         | BULT        |            | IN    |

|         |             |            |       |

|         |             |            |       |

|         |             |            |       |

|         |             |            |       |

|         |             |            |       |

|         |             |            |       |

# CONTENTS

- 1. Numbering System

- 2. General Specification

- 3. Absolute Maximum Rating

- 4. Electrical Characteristics

- 5. Optical Characteristics

- 6. Interface Pin Function

- 7. Drawing & Block Diagram

- 8. US2066 Controller Data

- 9. CGROM& CGRAM

- 9.1 CGROM character code

- 9.2 CGRAM

- 10. Quality Assurance

- 11. Reliability

- 12. Precautions for Handling

- **13. Precautions for Electrical**

- 14. Precautions for Storage

BOLYMIN

|        | _        | _      | _   | _         | _        | _        | _        |          | BOLY     | MIN       |

|--------|----------|--------|-----|-----------|----------|----------|----------|----------|----------|-----------|

| 1. Nun | nberin   | ig Sys | tem |           |          |          |          |          |          |           |

|        | <u>B</u> | Ľ      |     | <u>A1</u> | <u>W</u> | <u>R</u> | <u>N</u> | <u>B</u> | <u>U</u> | <u>\$</u> |

|        |          |        |     |           |          |          |          |          |          |           |

|        | 0        | 1      | 2   | 3         | 4        | 5        | 6        | 7        | 8        | 9         |

|        |          |        |     |           |          |          |          |          |          |           |

| 0 | Brand                                             | Bolymin                                                                            |                                                                           |

|---|---------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 1 | Module Type                                       | L=PLED/OLED                                                                        |                                                                           |

| 2 | Format                                            | 2002=20 characters, 2 lines<br>12232= 122 x 32 dots                                |                                                                           |

| 3 | Version No.                                       | A1 type                                                                            |                                                                           |

| 4 | LCD Color                                         | L=OLED/Green<br>W=OLED/White<br>K= OLED/Blue                                       | E=OLED/Yellow<br>R=OLED/Red                                               |

| 5 | LCD Type                                          | R=positive/reflective                                                              |                                                                           |

| 6 | Backlight type/color                              | N=No backlight                                                                     |                                                                           |

| 7 | CGRAM Font<br>(applied only on<br>character type) | J=English/Japanese Font<br>E=English/European Font<br>B= English/Japanese/European | C=English/Cyrillic Font<br>H=English/Hebrew Font<br>A=English/Arabic Font |

| 8 | View Angle/ Operating<br>Temperature              | U=Bottom/Ultra wide Temperature                                                    |                                                                           |

| 9 | Special Code                                      | n=positive voltage for LCD                                                         | \$=RoHS                                                                   |

# **2.General Specification**

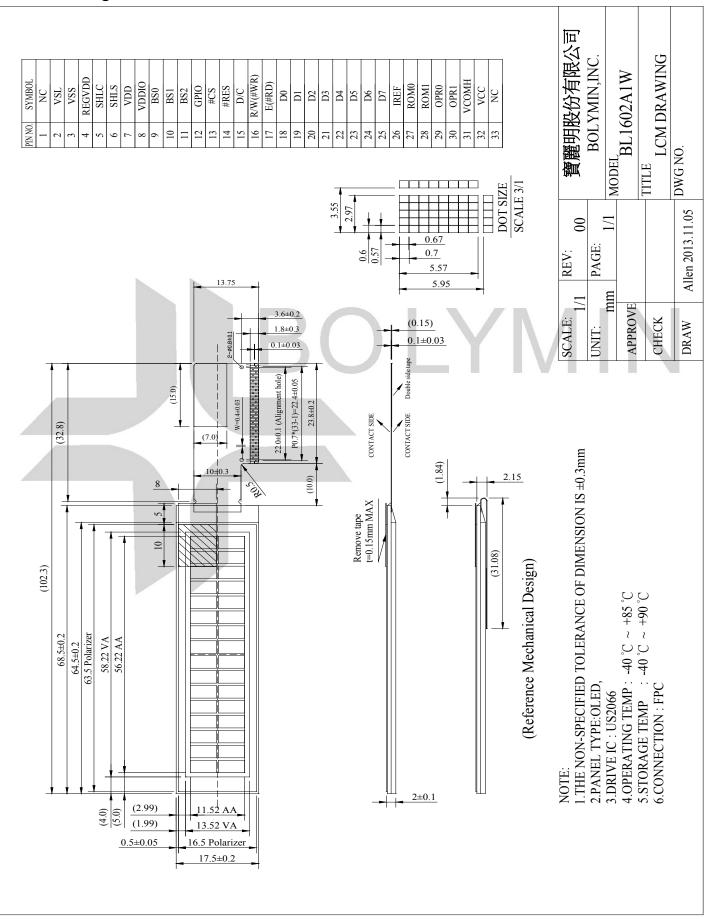

(1) Mechanical Dimension

| Item                    | Standard Value         | Unit |

|-------------------------|------------------------|------|

| Number of Characters    | 16 characters ×2 Lines | dots |

| Panel dimension (L*W*H) | 68.5 x 17.5 x 2.0      | mm   |

| View area               | 58.22 x 13.52          | mm   |

| Active area             | 56.22 x 11.52          | mm   |

| Dot size                | 0.57 x 0.67            | mm   |

| Dot pitch               | 0.60 x 0.70            | mm   |

| Character size (L x W)  | 2.97 x 5.57            | mm   |

| Character pitch (L x W) | 3.55 x 5.95            | mm   |

BOLYMIN

30 LYMIN

(2) Controller IC: US2066 Controller

| Item                  | Symbol | Condition             | Min     | Max     | Unit |

|-----------------------|--------|-----------------------|---------|---------|------|

| Operating Temperature | ТОР    |                       | -40     | +85     | °C   |

| Storage Temperature   | TST    |                       | -40     | +90     | °C   |

| Supply Voltage(Logic) | VDD    |                       | -0.3    | 6.0     | V    |

| Input Voltage         | VI     |                       | GND-0.3 | VDD+0.3 | V    |

| Operating life time   |        | 120 cd/m <sup>2</sup> | 30000   |         | Hrs  |

| Operating life time   |        | 100 cd/m <sup>2</sup> | 50000   |         | Hrs  |

Note:(A) Under VCC = 12V, Ta = 25°C, 50% RH.

- (B) Life time is defined the amount of time when the luminance has decayed to less than 50% of the initial measured luminance.

- (C) Lifetime should be counted once shipping out from our warehouse . But the exact lifetime must depend on customer's operation enviornment and application.

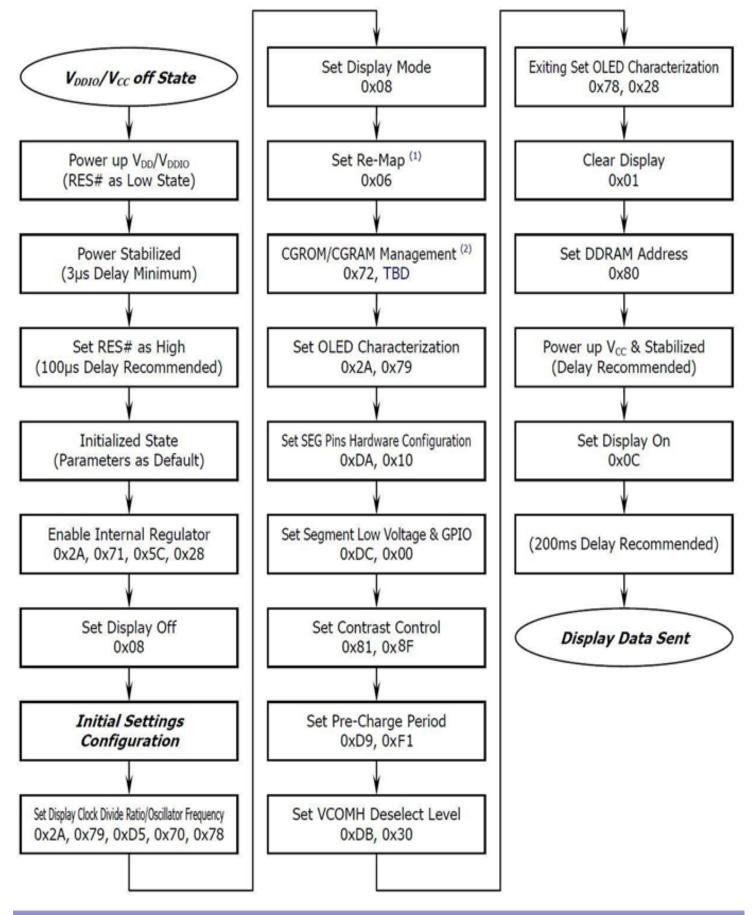

- \* Software configuration follows Initialization.

End of lifetime is specified as 50% of initial brightness reached. The average operating lifetime at room temperature is estimated by the accelerated operation at high temperature conditions.

# **4.Electrical Characteristics**

(Ta=25°C)

| Item                   | Symbol          | Condition | Min.         | Тур. | Max.         | Unit |

|------------------------|-----------------|-----------|--------------|------|--------------|------|

| Supply Voltage (VDDIO) | VDDIO           | —         | 4.5          | 5.0  | 5.5          | V    |

| Supply Voltage (VCC)   | VCC             |           | 11.5         | 12.0 | 12.5         | V    |

| Input High Vol         | V <sub>IH</sub> | —         | $0.8 V_{DD}$ | _    | $V_{DD}$     | V    |

| Input Low Vol          | V <sub>IL</sub> | _         | 0            |      | $0.2V_{DD}$  | V    |

| Output High Vol        | V <sub>OH</sub> | _         | $0.9V_{DD}$  | _    | _            | V    |

| Output Low Vol.        | V <sub>OL</sub> | _         | _            | _    | $0.1 V_{DD}$ | V    |

| Supply Current(White)  | IDD             | _         |              | 33   | 40           | mA   |

XVDD= 5.0V, VCC = 12.0V, 100% Display Area Turn on. Display color=White .

# 5. Optical Characteristics

| Optical Characteris    | stics       | 30          | LY          | Μ     | IN |

|------------------------|-------------|-------------|-------------|-------|----|

| Item                   | Min.        | Тур.        | Max.        | Unit  |    |

| View Angle             | Free        |             | _           | deg   |    |

| Dark Room contrast     | _           | >10000:1    | _           | _     |    |

| Pixel Luminance        | 100         | 120         |             | cd/m2 |    |

| CIE x,y (Color: White) | (0.25,0.27) | (0.29,0.31) | (0.33,0.35) |       |    |

# **6.Interface Pin Function**

| Pin No | Symbol | I/O | Descrip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | otion                                                                                                       |                                                                           |                                                                  |             |  |  |

|--------|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------|-------------|--|--|

| 1      | NC     | -   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                             |                                                                           |                                                                  |             |  |  |

| 2      | VSL    | Р   | This is segment voltage reference pin.<br>When external $V_{SL}$ is not used, this pin should be left open.<br>When external $V_{SL}$ is used, this pin should connect with resistor and diode to ground.                                                                                                                                                                                                                                                                                                |                                                                                                             |                                                                           |                                                                  |             |  |  |

| 3      | VSS    | Р   | This is a ground pin. It also acts as a re<br>OEL driving voltages, and the analog<br>external ground.                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                             |                                                                           |                                                                  |             |  |  |

| 4      | REGVDD | Ι   | This is internal V $_{DD}$ regulator selection pin in 5V I/O application mod<br>When this pin is pulled "I ow" internal V $_{DD}$ regulator is disabled                                                                                                                                                                                                                                                                                                                                                  |                                                                                                             |                                                                           |                                                                  |             |  |  |

| 5      | SHLC   | Ι   | This pin is used to determine COM output scanning direction. It can still be programmable and defined by fundamental command.                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                             |                                                                           |                                                                  |             |  |  |

| 6      | SHLS   | Ι   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | change the mapping between the display data column<br>ment driver. It can still be programmable and defined |                                                                           |                                                                  |             |  |  |

| 7      | VDD    | Р   | This is a voltage supply pin which is supplied externally or regulated internally. A capacitor should be connected between this pin and V <sub>SS</sub> under all circumstances. When internal V <sub>DD</sub> is disabled, this is a power input pin. It must be connected to V <sub>DDIO</sub> or external source and always be equal to or lower than V <sub>DDIO</sub> . (Low Voltage I/O Application) When internal V <sub>DD</sub> is enabled, it is regulated internally from V <sub>DDIO</sub> . |                                                                                                             |                                                                           |                                                                  |             |  |  |

| 8      | VDDIO  | Р   | This is a voltage supply pin. It should<br>voltage level and must be connected to                                                                                                                                                                                                                                                                                                                                                                                                                        | match with                                                                                                  | the MCU                                                                   | interface                                                        |             |  |  |

| 9      | BS0    |     | These pins are MCU interface selectio<br>$I^2C$                                                                                                                                                                                                                                                                                                                                                                                                                                                          | n input. S<br>BS0                                                                                           | See the follo<br>BS1                                                      | owing table:<br>BS2                                              |             |  |  |

| 10     | BS1    | I   | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Serial<br>4-bit 68XX Parallel                                                                               | 0<br>0<br>1                                                               | 1<br>0<br>0                                                      | 0<br>0<br>1 |  |  |

| 11     | BS2    |     | 4-bit 80XX Parallel<br>8-bit 68XX Parallel<br>8-bit 80XX Parallel                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1<br>0<br>0                                                                                                 | 1<br>0<br>1                                                               | 1<br>1<br>1                                                      |             |  |  |

| 12     | GPIO   | I/O | This pin could be left open individuall<br>outputted. It is able to use as the extern<br>enabled/disabled control or other appli                                                                                                                                                                                                                                                                                                                                                                         | y or have s<br>nal DC/DC                                                                                    |                                                                           |                                                                  |             |  |  |

| 13     | CS#    | Ι   | This pin is the chip select input. The c<br>communication only when CS# is pull                                                                                                                                                                                                                                                                                                                                                                                                                          | hip is enabl                                                                                                | ed for MC                                                                 | U                                                                |             |  |  |

| 14     | RES#   | Ι   | This pin is reset signal input. When the chip is executed. Keep this pin pull his                                                                                                                                                                                                                                                                                                                                                                                                                        | e pin is low                                                                                                |                                                                           |                                                                  |             |  |  |

| 15     | D/C#   | Ι   | This pin is Data/Command control pin<br>input at D7~D0 will be interpreted as<br>pulled low, the input at D7~D0 will be<br>register. In I <sup>2</sup> C mode, this pin acts as<br>When serial interface mode is selected<br>ss . For detail relationship to MCU inter<br>Timing Characteristics Diagrams.                                                                                                                                                                                               | . When the<br>display data<br>transferred<br>SA0 for sla<br>l, this pin m                                   | pin is pulle<br>a. When the<br>d to the con<br>ave address<br>oust be com | ed high, the<br>e pin is<br>nmand<br>s selection.<br>nected to V |             |  |  |

|    |       |     |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                          | <b><i><b>T</b>r</i></b>                      |                                                                              |  |  |  |  |

|----|-------|-----|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------------|--|--|--|--|

| 16 | R/W#  | Ι   | microprocess<br>input. Pull th<br>write mode. V<br>Write (WR#)<br>pulled low ar | CU interface inputes<br>or, this pin will be<br>is pin to "High" for<br>When 80XX interf<br>input. Data write<br>and the CS# is pulle<br>pin must be connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | used as Read/<br>r read mode an<br>ace mode is sel<br>operation is ini<br>d low. When se | Write (F<br>d pull i<br>ected, t<br>tiated w | R/W#) selection<br>t to "Low" for<br>his pin will be the<br>then this pin is |  |  |  |  |

| 17 | E/RD# | Ι   | microprocess<br>operation is i<br>low. When co<br>Read (RD#) s<br>pulled low ar | nitiated when this<br>onnecting to an 80<br>signal. Data read on<br>d CS# is pulled lo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | used as the En<br>pin is pulled hi<br>XX-microproce<br>peration is initi<br>w.           | able (E<br>gh and<br>essor, th<br>ated wh    | ) signal. Read/write<br>the CS# is pulled<br>is pin receives the             |  |  |  |  |

| 18 | D0    |     |                                                                                 | e 8-bit bi-direction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                          |                                              |                                                                              |  |  |  |  |

| 19 | D1    |     | 1                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                          |                                              | ted, D0 will be the                                                          |  |  |  |  |

| 20 | D2    |     |                                                                                 | nput SCLK; D1 with the second se |                                                                                          |                                              |                                                                              |  |  |  |  |

| 21 | D3    |     |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                          |                                              |                                                                              |  |  |  |  |

| 22 | D4    | I/O |                                                                                 | D1 should be tired together and serve as SDA <sub>OUT</sub> , SDA IN in application and D0 is the serial clock input, SCL. Unused pins must be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                          |                                              |                                                                              |  |  |  |  |

| 23 | D5    |     | connected to                                                                    | V <sub>SS</sub> except.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                          |                                              |                                                                              |  |  |  |  |

| 24 | D6    |     |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                                                                        |                                              |                                                                              |  |  |  |  |

| 25 | D7    |     |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                          |                                              |                                                                              |  |  |  |  |

| 26 | IREF  | Ι   |                                                                                 | gment current refe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                          |                                              |                                                                              |  |  |  |  |

| 20 | INCLA | 1   |                                                                                 | tween this pin and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                          |                                              |                                                                              |  |  |  |  |

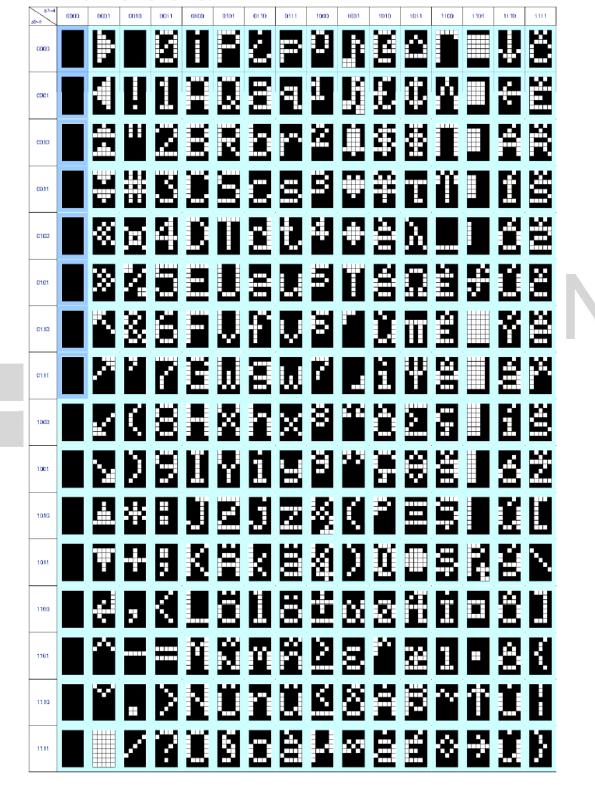

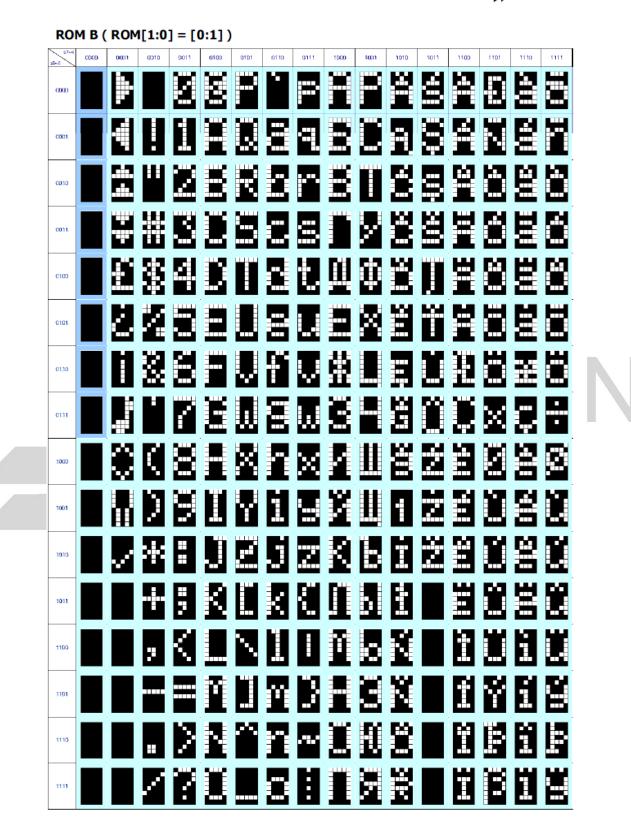

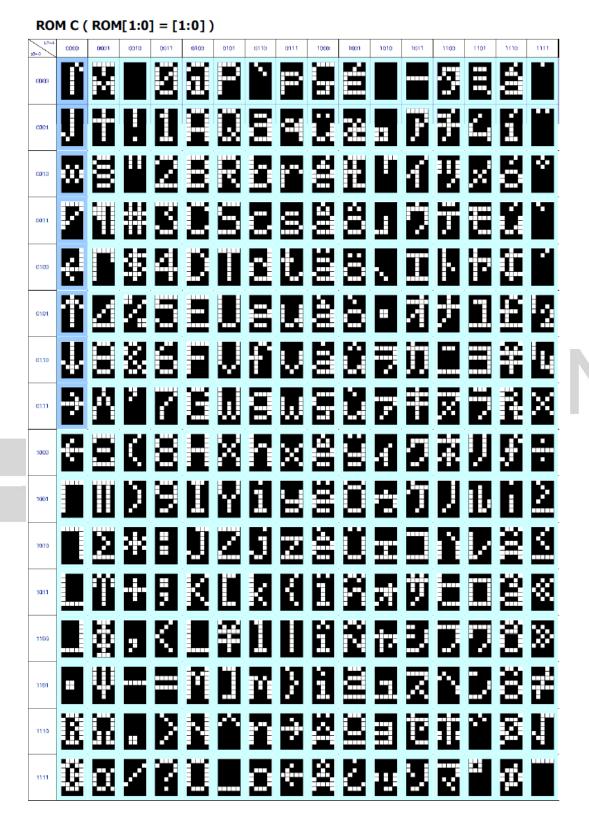

|    |       |     | following tab                                                                   | e used to select the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | e appropriate cl                                                                         | naracter                                     | ROM. See the                                                                 |  |  |  |  |

| 27 | ROM0  |     |                                                                                 | ROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                        | RO                                           | OM1                                                                          |  |  |  |  |

|    |       | I   | ROM A                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •                                                                                        | 0                                            |                                                                              |  |  |  |  |

|    |       |     | ROM B                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                          | 0                                            |                                                                              |  |  |  |  |

| 28 | ROM1  |     | ROMC                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                          | 1                                            |                                                                              |  |  |  |  |

|    |       |     | It can still be                                                                 | programmable an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | d defined by ex                                                                          | tended                                       | command.                                                                     |  |  |  |  |

|    |       |     |                                                                                 | re used to manage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                          | umber c                                      | of character                                                                 |  |  |  |  |

| 29 | OPR0  |     |                                                                                 | e the following tab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                          |                                              |                                                                              |  |  |  |  |

|    |       |     | CGROM<br>240                                                                    | CGRAM<br>8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | OPR0<br>0                                                                                |                                              | OPR1<br>0                                                                    |  |  |  |  |

|    |       | I   | 240                                                                             | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                        |                                              | 0                                                                            |  |  |  |  |

| 20 | ODD 1 |     | 250                                                                             | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                                                                        |                                              | 1                                                                            |  |  |  |  |

| 30 | OPR1  |     | 256                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                        |                                              | 1                                                                            |  |  |  |  |

|    |       |     |                                                                                 | programmable an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5                                                                                        |                                              |                                                                              |  |  |  |  |

| 31 | VCOMH | Р   | -                                                                               | e input pin for the<br>pacitor should be co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | • 1                                                                                      | •                                            |                                                                              |  |  |  |  |

| 32 | VCC   | Р   | This is the m                                                                   | ost positive voltag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                          |                                              |                                                                              |  |  |  |  |

|    |       |     | connected to                                                                    | external source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                          |                                              |                                                                              |  |  |  |  |

| 33 | NC    | -   | -                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                          |                                              |                                                                              |  |  |  |  |

# MCU interface assignment under different bus interface mode

| Pin Name   | Data/ | Data/Command interface Control Signal          |         |     |         |     |     |     |      |     |     |

|------------|-------|------------------------------------------------|---------|-----|---------|-----|-----|-----|------|-----|-----|

| Interface  | DB7   | DB6                                            | DB5     | DB4 | DB3     | DB2 | DB1 | DB0 | Е    | R/W | RS  |

| 6800,8-bit |       |                                                |         | Γ   | DB[7:0] |     |     |     | Е    | R/W | RS  |

| 8080,8-bit |       |                                                |         | Γ   | DB[7:0] |     |     |     | /RD  | /WR | RS  |

| SPI        |       | Tied LOW     SOD     SID     SCLK     Tied LOW |         |     |         |     |     |     |      |     |     |

| I2C        |       | Γ                                              | fied LO | W   |         | SDO | SDA | SCL | Tied | LOW | SA0 |

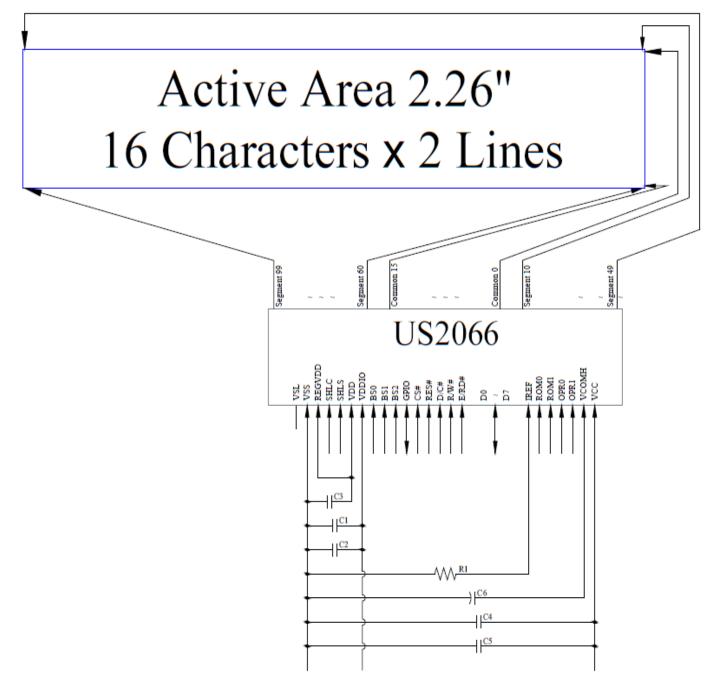

# 7. Drawing & Block Diagram

7.1 Drawing

7.2 BLOCK DIAGRAM

BOLYMIN

MCU Interface Selection: BS0, BS1 and BS2 Pins connected to MCU interface: CS#, RES#, D/C#, R/W#, E/RD#, and D0~D7 \* SHLC, SHLC, ROM0, ROM1, OPR0 and OPR1 should be configured.

C1, C4:  $0.1\mu$ F C2:  $4.7\mu$ F C3:  $1\mu$ F C5:  $10\mu$ F C6:  $4.7\mu$ F / 25V Tantalum Capacitor R1:  $470k\Omega$ , R1 = (Voltage at IREF - VSS) / IREF

# 8.US2066 Controller Data

# 8.1 MPU Parallel 6800-series Interface

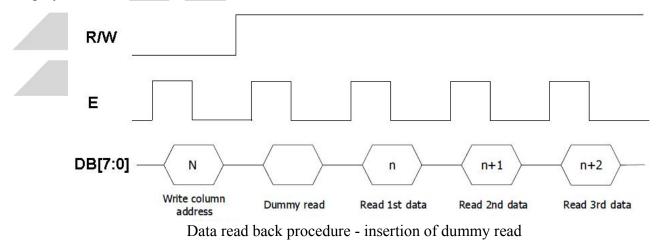

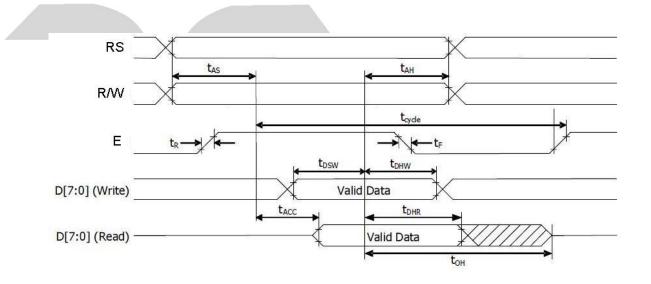

The parallel interface consists of 8 bi-directional data pins (DB[7:0]), R/W, RS, E. A LOW in R/W indicates WRITE operation and HIGH in R/W indicates READ operation. A LOW in RS indicates COMMAND read/write and HIGH in RS indicates DATA read/write. The E input serves as data latch signal. Data is latched at the falling edge of E signal.

| Function      | E | R/W | RS |

|---------------|---|-----|----|

| Write command | Ļ | L   | L  |

| Read status   | Ļ | н   | L  |

| Write data    | Ţ | L   | н  |

| Read data     | Ļ | Н   | н  |

Control pins of 6800 interface

In order to match the operating frequency of display RAM with that of the microprocessor, some pipeline processing is internally performed which requires the insertion of a dummy read before the first actual display data read.

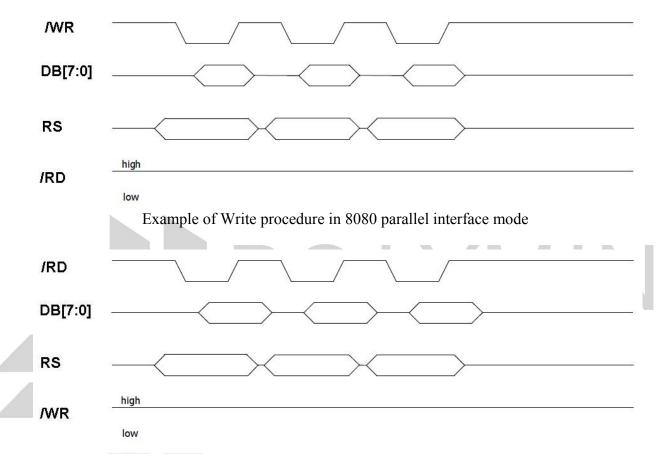

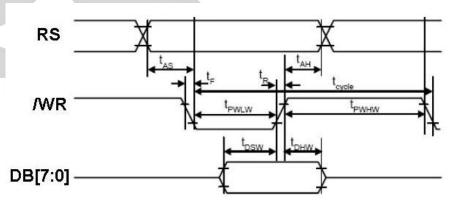

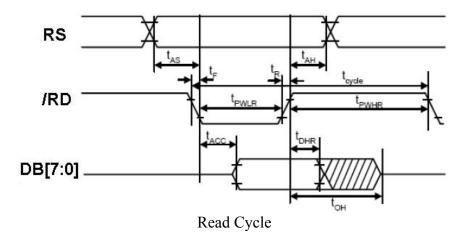

# 8.2 MPU Parallel 8080-series Interface

The parallel interface consists of 8 bi-directional data pins (DB[7:0]), /RD ,/WR, RS.

- A LOW in RS indicates COMMAND read/write and HIGH in RS indicates DATA read/write.

- A rising edge of /RD input serves as a data READ latch signal.

- A rising edge of /WR input serves as a data/command WRITE latch signal.

Example of Read procedure in 8080 parallel interface mode

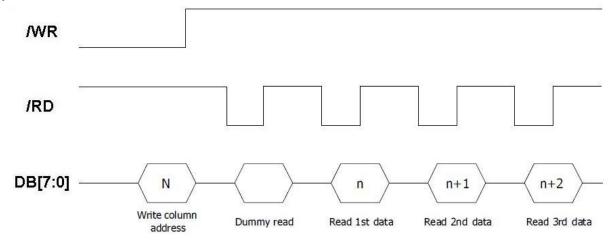

In order to match the operating frequency of display RAM with that of the microprocessor, some pipeline processing is internally performed which requires the insertion of a dummy read before the first actual display data read. This is shown below.

# 8.3 Serial Interface

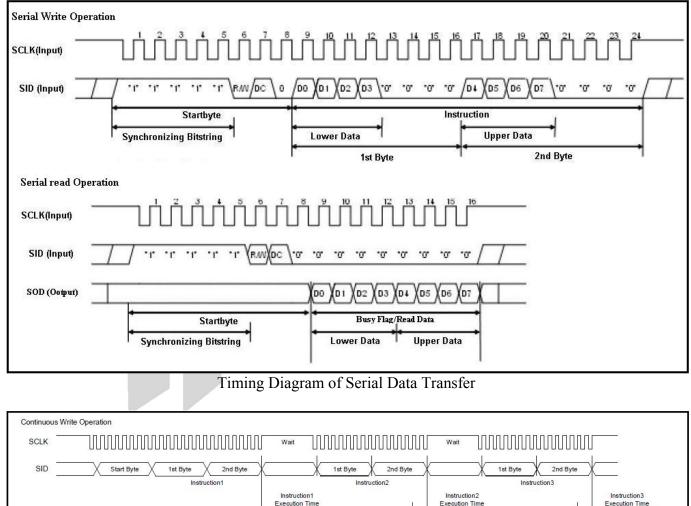

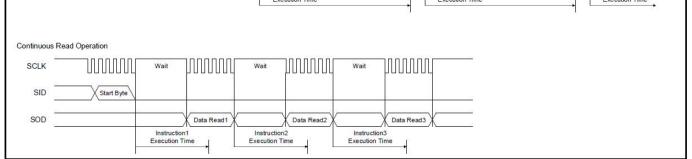

When serial interface mode (SPI) is started, all the three ports, SCLK(DB0), SID(DB1) and SOD(DB2) are used. Before transfer real data, start byte has to be transferred. It is composed of succeeding five "High" bits, read write control bit (R/W), register selection bit (RS) and end bit that indicates the end of start byte. Whenever succeeding five "High" bits are detected by US2066, it makes serial transfer counter reset and ready to receive next information.

The next input data are register selection bit that determine which register will be used, and read write control bit that determine the direction of data. Then end bit is transferred, which must have "Low" value to show the end of start byte. (Refer to the two Figures below).

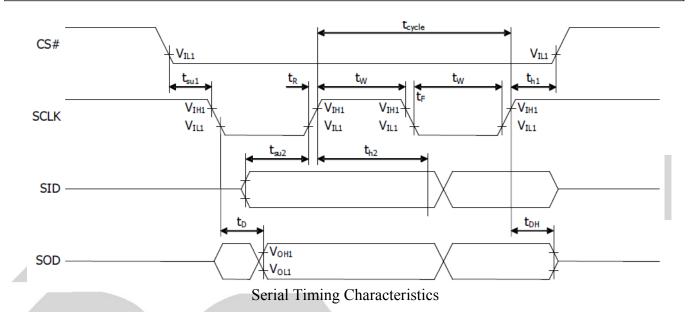

#### 8.3.1 Timing Diagram

Timing Diagram of Continuous Data Transfer

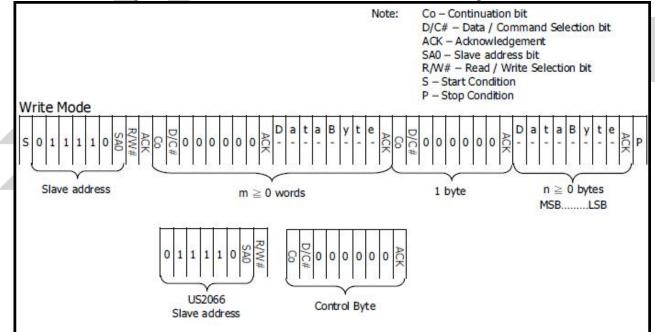

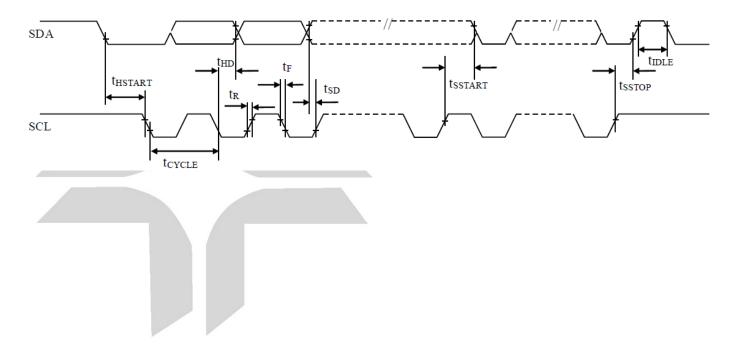

# 8.4 MCU I2C Interface

The I2C communication interface consists of slave address bit SA0, I2C-bus data signal SDA (SDAOUT/DB2 for output and SDAIN/DB1 for input) and I2C-bus lock signal SCL (DB0). BL2004AW has to recognize the slave address before transmitting or receiving any information by the I2C-bus. The device will respond to the slave address following by the slave address bit ("SA0" bit) and the read/write select bit ("R/W#" bit) with the following byte format,

| DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 1   | 1   | 1   | 1   | 0   | SA0 | R/W |

"SA0" bit provides an extension bit for the slave address. Either "0111100" or "0111101" can be selected as the Slave address of BL2004AWLRNEHn20c.RS pin acts as SA0 for slave address selection.

R/W bit is used to determine the operation mode of the I2C-bus interface.

R/W=1, it is in read mode.

R/W=0, it is in write mode.

#### I2C-bus Write data

Please refer to Figure below for the write mode of I2C bus in chronological order.

I2C-bus data format

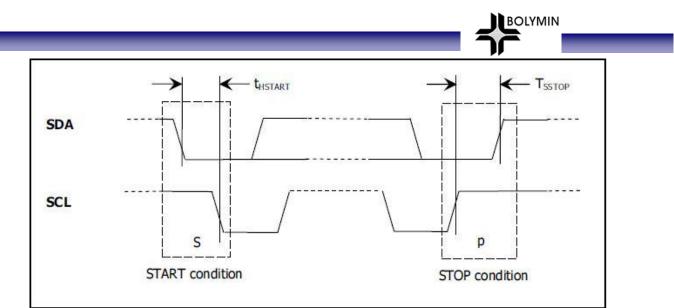

**Definition of the Start and Stop Condition**

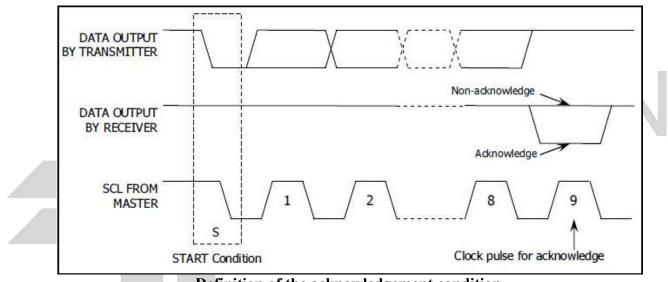

Definition of the acknowledgement condition

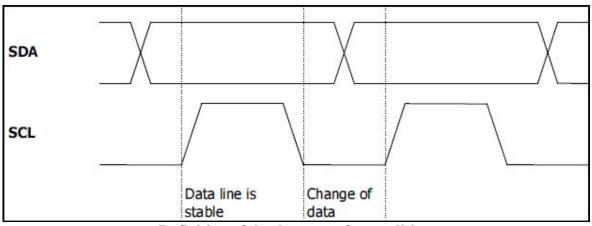

The data bit, which is transmitted during each SCL pulse, must keep at a stable state within the "HIGH" period of the clock pulse. Please refer to the Figure below for graphical representations. Except in start or stop conditions, the data line can be switched only when the SCL is LOW.

Definition of the data transfer condition

# **8.5 Timing Characteristics**

6800 MPU Interface

| Symbol             | Parameter                                  | Min          | Max | Unit |

|--------------------|--------------------------------------------|--------------|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time (write cycle)             | 400          | -   | ns   |

| tAS                | Address Setup Time                         | 13           | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time                          | 17           | -   | ns   |

| t <sub>cs</sub>    | Chip Select Time                           | 0            | - 1 | ns   |

| t <sub>CH</sub>    | Chip Select Hold Time                      | 0            | -   | ns   |

| t <sub>DSW</sub>   | Write Data Setup Time                      | 35           | -   | ns   |

| t <sub>DHW</sub>   | Write Data Hold Time                       | 18           | -   | ns   |

| t <sub>DHR</sub>   | Read Data Hold Time                        | 13           | -   | ns   |

| t <sub>OH</sub>    | Output Disable Time                        | 10           | 90  | ns   |

| t <sub>ACC</sub>   | Access Time (RAM)                          | 1547         | 105 | ns   |

|                    | Access Time (command)                      | -            | 125 | ns   |

| PW <sub>CSL</sub>  | Chip Select Low Pulse Width (read RAM)     | 250          | 2   | ns   |

|                    | Chip Select Low Pulse Width (read Command) | 250          | -   | ns   |

|                    | Chip Select Low Pulse Width (write)        | 50           | 2   | ns   |

| PW <sub>CSH</sub>  | Chip Select High Pulse Width (read)        | 155          | -   | ns   |

| entral PAG Tabri   | Chip Select High Pulse Width (write)       | 55           | -   | ns   |

| t <sub>R</sub>     | Rise Time                                  | -            | 15  | ns   |

| t <sub>F</sub>     | Fall Time                                  | 1 <u>-</u> 2 | 15  | ns   |

| 8080 | MPU | Interface |

|------|-----|-----------|

|------|-----|-----------|

| Symbol             | Parameter                                                     | Min | Тур | Max | Unit |

|--------------------|---------------------------------------------------------------|-----|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time (write cycle)                                | 400 | -   | -   | ns   |

| t <sub>AS</sub>    | Address Setup Time                                            | 13  | -   | -   | ns   |

| t <sub>AH</sub>    | Address Hold Time                                             | 17  | -   | -   | ns   |

| t <sub>cs</sub>    | Chip Select Time                                              | 0   | -   |     | ns   |

| t <sub>CSH</sub>   | Chip select hold time to read signal                          | 0   | -   | -   | ns   |

| t <sub>CSF</sub>   | Chip select hold time                                         | 0   | -   | 127 | ns   |

| t <sub>DSW</sub>   | Write Data Setup Time                                         | 35  | -   | -   | ns   |

| t <sub>DHW</sub>   | Write Data Hold Time                                          | 18  | -   | -   | ns   |

| t <sub>DHR</sub>   | Read Data Hold Time                                           | 13  | -   | -   | ns   |

| toH                | Output Disable Time                                           | 10  | -   | 70  | ns   |

| tACC               | Access Time (RAM)                                             |     |     | 125 | ns   |

|                    | Access Time (command)                                         | -   | -   | 125 | ns   |

| PW <sub>CSL</sub>  | Chip Select Low Pulse Width (read RAM) - t <sub>PWLR</sub>    | 250 | -   | -   | ns   |

|                    | Chip Select Low Pulse Width (read Command) - t <sub>PMR</sub> | 250 | -   | -   | ns   |

|                    | Chip Select Low Pulse Width (write) - t <sub>PWLW</sub>       | 50  | 2   | -   | ns   |

| PW <sub>CSH</sub>  | Chip Select High Pulse Width (read) - t <sub>PWHR</sub>       | 155 | -   | -   | ns   |

|                    | Chip Select High Pulse Width (write) - t <sub>PWHW</sub>      | 55  | -   | -   | ns   |

| t <sub>R</sub>     | Rise Time                                                     | - 1 | -   | 15  | ns   |

| t <sub>F</sub>     | Fall Time                                                     | - 1 | -   | 15  | ns   |

Write Cycle

# SPI MPU Interface

| Symbol                          | Parameter                      | Min | Тур | Max | Unit |

|---------------------------------|--------------------------------|-----|-----|-----|------|

| t <sub>c</sub>                  | Serial clock cycle time        | 1   | -   | 20  | us   |

| t <sub>r</sub> , t <sub>f</sub> | Serial clock rise/fall time    | -   | -   | 15  | ns   |

| t <sub>w</sub>                  | Serial clock width (high, low) | 400 | -   | -   | ns   |